Synopsys SLM Path Margin Monitor IP

Measure Timing Margin of Actual Functional Paths In-Test or In-Field

The Path Margin Monitor (PMM) solution consists of multiple PMM units, a PMM controller, and associated software and EDA automation. PMM IP is a building block for the PMM solution which is also supported by an automated implementation flow from Synopsys. Path selection logic, RTL configuration and generation, connecting to functional and/or test paths, synthesis, implementation, timing validation and path qualification are the key functions addressed by the EDA automation provided. Associated software allows the data generated from the PMM solution to be effectively analyzed and allow precise decisions made based on those insights.

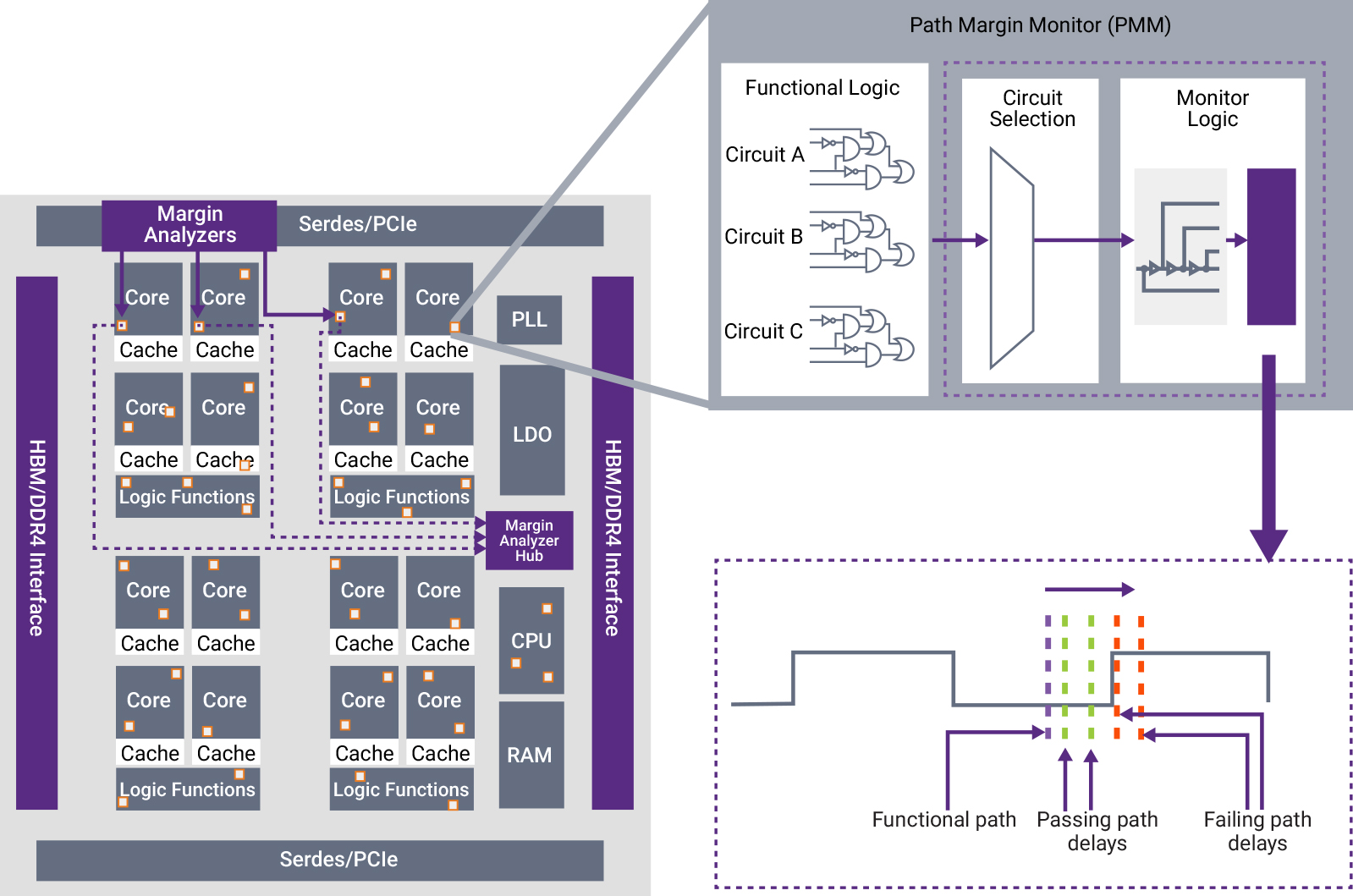

Figure 1: Synopsys Path Margin Monitor

Path Margin Monitor Unit

The PMM unit enables timing margin measurement of selected path in-test or mission mode. Timing margin is a key indicator of silicon structural health. Each PMM can handle multiple end points for measurement and each PMM controller can support multiple PMMs. On a single chip you can place numerous PMMs without much area overhead, providing very valuable data which can be analyzed for insights to optimize any phase of silicon lifecycle. EDA and software automation along with path selection logic plays a crucial role in making PMMs practical.

Path Margin Monitor Controller

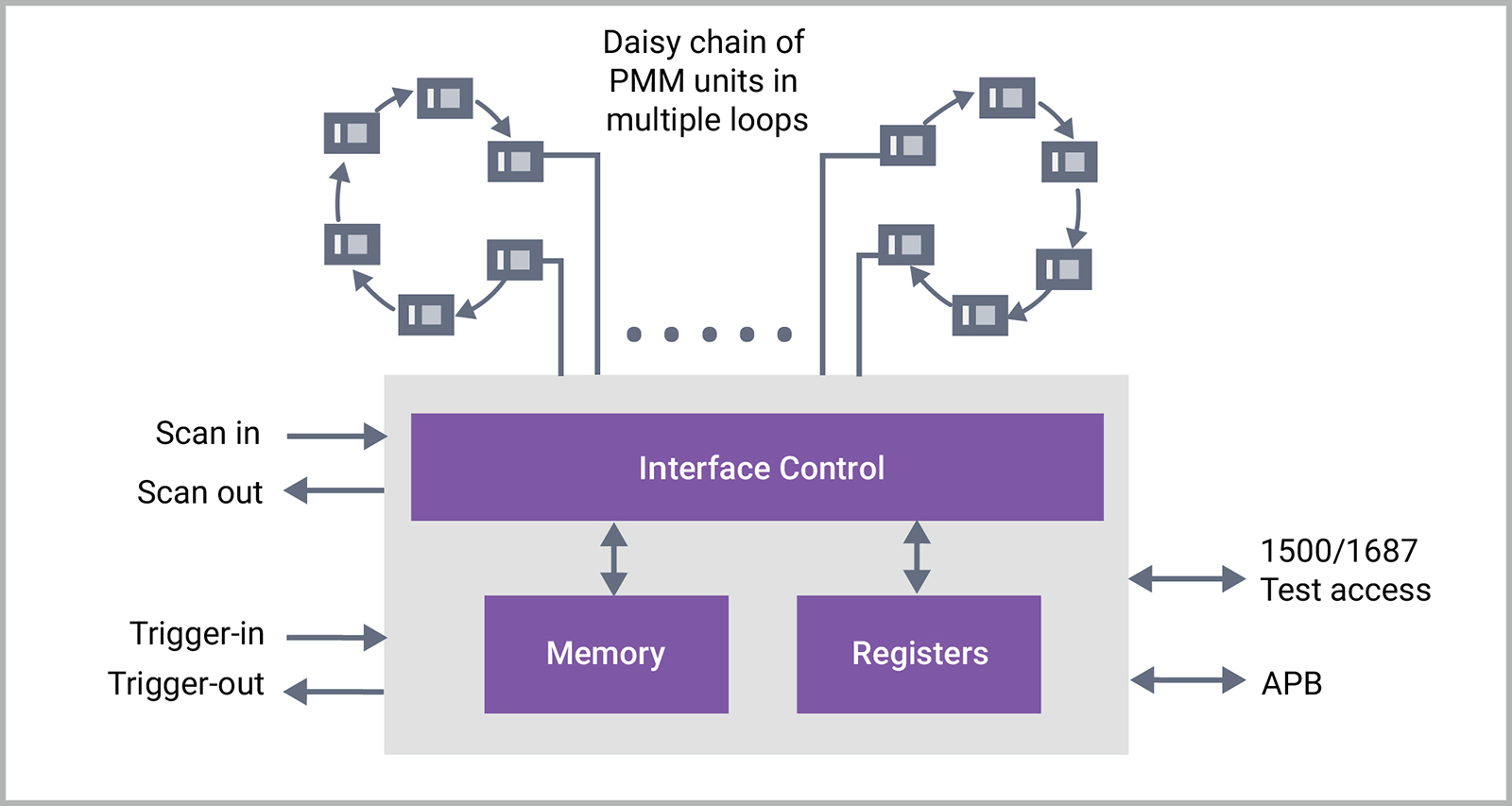

Figure 2: Synopsys Path Margin Monitor Controller

- Autonomous operation

- PMM controller manages the configuration and data collection of the PMM units

- Internal memory storage for configuration and results

- Support multiple groups of PMM units based on power/clock/functional domains

- Provide first level data processing and filtering

- Track number of failed PMM units

- Compare results between consecutive runs

- Provide 1500 and APB interface to connect to test fabric or SoC functional fabric

Use Cases

- Silicon to design

- Supply margin improvement

- In-field chip performance optimization

- Reliability analysis

- Highly configurable IP with automated EDA flow

- Monitor test or functional paths

- Integrates into existing scan chain

- Real time reporting for analytics

- Optimize silicon performance based on actual margins available

![]() Synopsys Silicon Lifecycle Management (SLM) Path Margin Monitors

Synopsys Silicon Lifecycle Management (SLM) Path Margin Monitors