Synopsys ARC nSIM

The Synopsys ARC® nSIM Instruction Set Simulator provides an instruction accurate processor model for the Synopsys ARC processor families. Such processor models take the software development out of your products’ critical path by enabling an early start as well as increased efficiency through enhanced visibility and control. The nSIM models provide a complete and accurate hardware/software interface model of the ARC processors that guarantees binary compatibility of product code between the simulation platform and the hardware. The model is configurable and supports ARC and ARC-V processors, including the 32-bit ARC-V RMX embedded processors, the 32-bit ARC-V RHX real-time processors, the 64-bit ARC-V RPX host processors. It also supports ARC Processors, from the high-speed ARC HS Family, the deeply embedded ARC EM Family and the ARC VPX DSP Family, to the general-purpose ARC 600 Family and the ARC 700 Family for high-performance applications.

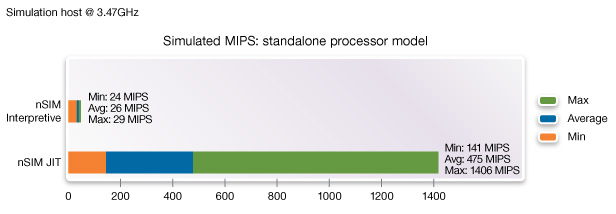

The nSIM Pro simulator comes with a state-of-the-art JIT compilation engine that leverages the capabilities of multi-core simulation hosts by offloading JIT translation threads from the core that is running the simulation reducing the JIT compilation overhead and significantly speeding up simulation performance. Embedded Microprocessor Benchmark Consortium (EEMBC) benchmarks on a simulation host running at 3.47 GHz show an 18X speed increase, on average, when JIT mode is activated and JIT translation is offloaded to a separate core of the simulation host. As a result, an average performance of 475 MIPS is reached across all 34 tests of the test suite. And over 1,400 MIPS is reached for the EEMBC bezier01 test that benefits most of the JIT activation.

In the case where a full 100% cycle accuracy is needed for final performance tweaking or verification, an ARC xCAM model can be used. These models are derived from the processor's Verilog to achieve 100% cycle accuracy.

| Interpretive | JIT | |

|---|---|---|

| Average speed | 20 MIPS | 475 MIPS |

| Instruction accuracy | 100% | 100% |

| Cycle accuracy | N/A | N/A |

| Software development & debug | YES | YES |

The nSIM processor model is delivered as a single DLL that integrates seamlessly with the MetaWare and GNU debuggers. The nSIM models come with an industry-standard OSCI TLM-2.0 SystemC interface to support their integration with OSCI standard peripheral models. In addition, the nSIM models implement the required interfaces for deployment in the Synopsys Virtualizer platform, a tool for the creation, assembly and execution of SystemC-based virtual prototypes for pre-silicon software development and software-driven verification.

Request Information or Order Synopsys ARC nSIM Pro

- Single product supporting instruction accurate modelling of Synopsys ARC Classic (ARC HS, ARC EM, ARC 600, ARC 700 and ARC AS200) and ARC-V (ARC RMX, ARC RHX and ARC RPX) families

- Accurate cycle-based (NCAM), interpretive and high-speed JIT-compilation (just-in-time) modelling variants

- Models for APEX processor extensions can be added as an extension DLL or as a separate SystemC component; automatically generated or handcrafted

- OSCI TLM-2.0 SystemC standard interface for SoC level modelling

- Synopsys Virtualizer and Platform Architect integration layers on top of SystemC interface provide access to advanced debugging and profiling capabilities offered by Synopsys SoC prototyping platforms

- Standard gdbserver protocol as well as optimized proprietary API for interfacing with a debugger

- Semihosting support with MetaWare Hostlink and standard RISC-V interfaces

- Available for 64-bit Windows and Linux simulation hosts

| Description: | ARC nSIM Instruction Set Simulator for ARC Processors |

| Name: | dw_arc_nsim |

| Version: | V-2024.03 |

| ECCN: | 3E991/NLR |

| STARs: | Open and/or Closed STARs |

| myDesignWare: | Subscribe for Notifications |

| Product Type: | DesignWare Cores |

| Documentation: | |

| Download: | arc_nSIM |

| Product Code: | 3355-0, 6782-0, 6787-0, 8111-0, 8112-0, 9217-0, 9500-0, A412-0, E035-0, F604-0 |