Cloud native EDA tools & pre-optimized hardware platforms

DesignWare IP for Commerce Applications

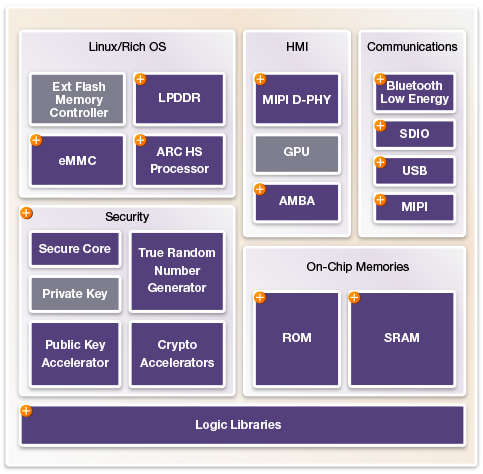

Overview

From bar code scanners, to cash registers and portable credit card terminals, digital commerce has dramatically improved the ability to track assets and exchange money and services. Security and long battery life are two important design considerations for these devices. Synopsys provides designers with a wide range of IP that addresses the features required for developing low power, secure SoCs for these applications.

Mouse over or tap to learn more about DesignWare IP solutions:

Bluetooth Low Energy

- Link Layer and PHY

- Operates below one volt supply

- Integrated security functions

- Supports the latest Bluetooth low energy standard

- Learn more >>

SDIO

- Compliant with the latest SD, SDIO and eMMC specifications

- SD/eMMC supports 1-bit, 4-bit and 8-bit cards

- Low power option with clock & power ON/OFF features

- Learn more >>

USB

- USB femtoPHY cuts area by 50%-.16mm2

- Proven USB controllers for rapid integration

- Support for power supply gating and ultra-low standby current

- Proven compatibility with USB 1.1 to USB 3.1 speeds

- Learn more >>

MIPI

- Interoperable DSI and CSI-2 Controllers

- Power-optimized D-PHY

- Low-power Gear3 M-PHY

- Compliant to standard specifications

- Learn more >>

SRAM

- High-density low leakage memory w/power reduction modes

- Ultra low voltage operation

- Deep sleep mode reduces leakage by 70%

- Long channel devices reduce active leakage

- Learn more >>

ROM

- Ultra low power anti-signature ROM

- Reduces leakage by up to 20%

- Learn more >>

AMBA

- Synthesizable AHB & AXI DMA Controllers

- Synthesizable IP for APB general purpose & advanced peripherals

- Includes GPIO, timers, RTC, RAP, WDT, I2C, I2S, UART and SSI

- Learn more >>

MIPI

- Interoperable DSI and CSI-2 Controllers

- Power-optimized D-PHY

- Low-power Gear3 M-PHY

- Compliant to standard specifications

- Learn more >>

LPDDR

- DDR PHY Compiler to optimize DDR IP configuration

- Supports auto disable of buffers, receivers & drivers to reduce power

- Supports x16 and x32 SDRAMs

- Learn more >>

eMMC

- Compliant with the latest SD, SDIO and eMMC specifications

- SD/eMMC supports 1-bit, 4-bit and 8-bit cards

- Low power option with clock & power ON/OFF features

- Learn more >>

ARC HS Processor

- High-performance 32-bit processors

- >3100 DMIPS@ 1.6 GHz, 60mW power, .15mm2 area

- Customized instructions to integrate user HW accelerators

- Learn more >>

Security

- Used to store user configuration, calibration & security data

- Security protocol accelerators and co-processors

- Embedded security IP modules establish secure hardware Root of Trust environments

- Secure boot and cryptography middleware

- Learn more >>

Logic Libraries

- Thick oxide “always-on” libraries for static power savings

- Multi-bit flops for dynamic power and area savings

- Power Optimization Kit minimizes core leakage

- Ultra low voltage operation (40% below Vddnom)

- Learn more >>

Highlights:

- DDR multiPHY IP combined with DesignWare Universal DDR digital controller and verification IP provides a complete multi-protocol DDR interface IP solution supporting LPDDR2/3

- MIPI CSI-2 and DSI controllers are compliant to specifications rev 1.2. Support 1 to 8 and 1 to 4 data lanes respectively with D-PHY PPI interface operating up to 2.5 Gbps per lane

- ADC with up to 14-bit resolution and 5 Msps conversion rates exceed leading on-chip implementations

- Multi-bit flops minimize clock loading, area and leakage, improving dynamic and static power

- Power Optimization Kits (POKs) for DesignWare Logic Libraries enable power consumption minimization while sustaining optimal performance

- Memory compilers with advanced power management features reduce leakage by up to 70%, controlled via a single pin. Provides low voltage down to 60% VddNom

- Ultra-low power anti-signature via ROM reduces leakage up to 20%

- Proven, certified USB 2.0 controllers and PHYs are easy to integrate and support Battery Charging with low-power features

- ARC HS processors deliver maximum performance efficiency (DMIPS/mW and DMIPS/mm2) and are ideally suited for embedded applications with high-speed data and signal processing requirements.

- The configurable and extensible instruction set of the ARC HS processors enables the tailoring of each instance for optimum balance of performance, power and area

- Compact Bluetooth low energy Link Layer and PHYs enable secure wireless connectivity with extended reach, and low power consumption for extended battery life targeting wearables and smart home applications

- Security IP including Public Key Accelerators, True Random Number Generators and security protocol accelerators and secure hardware root of trust protects against evolving threats

- SD/eMMC controller IP provides advanced features for SD, SDIO and eMMC with Command Queuing Engine

PODCASTS